# JVC SERVICE MANUAL

## PORTABL MINIDISC PLAYER

## XM-PX33BU XM-PX33WT

XM-PX33BU ----- BLUE XM-PX33WT ----- WHITE

### Contents

| Safety Precautions            | 1-2 |

|-------------------------------|-----|

| Preventing static electricity | 1-3 |

| Important for laser products  | 1-4 |

| Disassembly method            | 1-5 |

| Adjustment method 1-9            |

|----------------------------------|

| Maintenance of laser pickup 1-10 |

| Replacement of laser pickup 1-10 |

| Description of major ICs 1-11    |

### -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

- 5. Leakage currnet check (Electrical shock hazard testing) After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock. Do not use a line isolation transformer during this check.

- Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

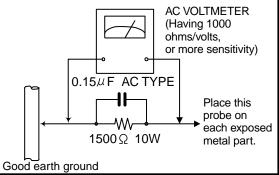

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a  $1,500\Omega$  10W resistor paralleled by a  $0.15\mu$ F AC-type capacitor between an exposed

metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meaus return path to the chassis. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

#### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

## Attention when MD pick up is exchanged

1. About the static electricity protection measures

The laser diode in the traverse unit (optical pick up) is easy to be destroyed by clothes and the human body to the electrified static electricity.

Please note the explosion by static electricity when repairing.

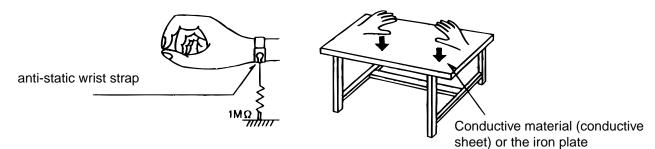

2. About the earth processing for the electrostatic destruction prevention

In the equipment which uses an optical pick up (laser diode), an optical pick up is destroyed by the static electricity of the work environment.

Please do the earth processing and work.

1) Earth of work stand

Please pull the conductive material (conductive sheet) or the iron plate to the depository

place of the traverse unit (optical pick up), and take the earth to ground.

2) Human body earth

Please use the anti-static wrist strap to exhaust the electrified static electricity to the human body.

- 3. Handling the optical pick up

- 1) Please return according to a correct procedure based on short processing after exchanging parts.

- 2) Do not use a tester to check the condition of the laser diode in the optical pick up .The tester 's internal power source can easily destroy the laser diode.

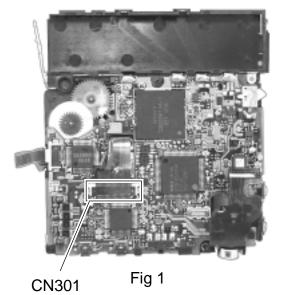

#### 4. Attention when unit is disassembled

Please refer to "Disassembling method" for how to detach .

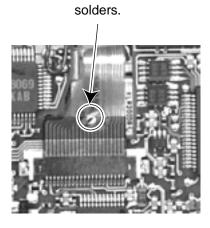

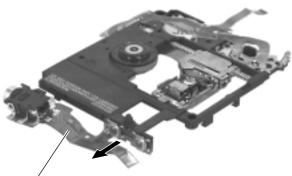

1) Please be sure to solder before a flexible wire is removed from connector CN301 on a main printed circuit board as shown in Figure 2.

if you removes without soldering.the MD picking up assembly might destroy

2) When installing , solder in the part of short round should be removed after a flexible wire is connected with CN301

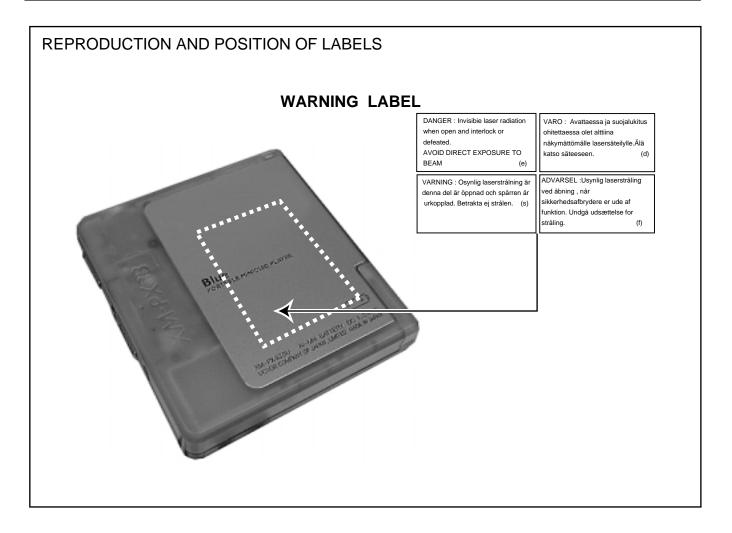

## Important for laser products

#### 1.CLASS 1 LASER PRODUCT

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

| VARNING · | Osynlig laserstrålning är denna del är öppnad     | ADVARSEL : Usynlig laserstråling ved åbning , når |

|-----------|---------------------------------------------------|---------------------------------------------------|

|           | och spårren är urkopplad. Betrakta ej strålen.    | sikkerhedsafbrydere er ude af funktion. Undgå     |

| VARO :    | Avattaessa ja suojalukitus ohitettaessa olet      | udsættelse for stråling.                          |

|           | alttiina näkymättömälle lasersäteilylle.Älä katso | ADVARSEL : Usynlig laserstråling ved åpning,når   |

|           | säteeseen.                                        | sikkerhetsbryteren er avslott. unngå utsettelse   |

|           |                                                   | for stråling.                                     |

|           |                                                   |                                                   |

## **Disassembly method**

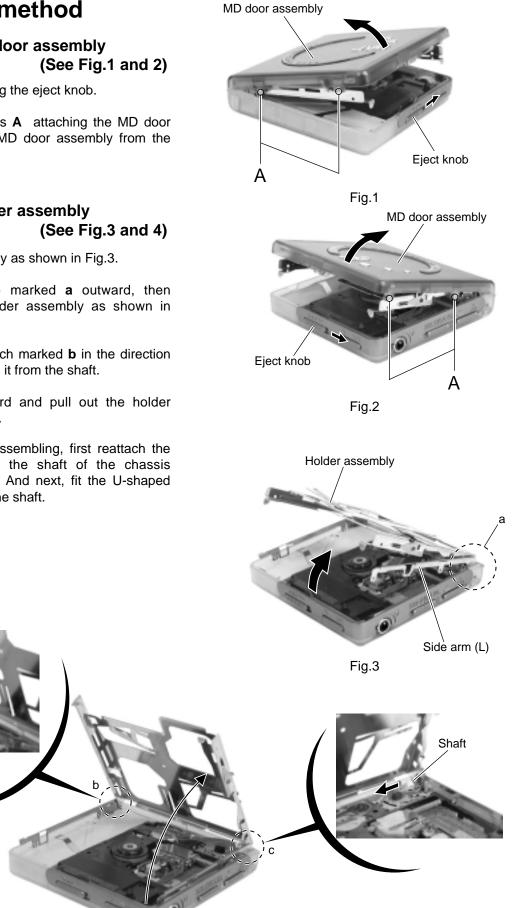

## ■ Removing the MD door assembly

- 1. Open the door by moving the eject knob.

- 2. Remove the four screws A attaching the MD door assembly. Detach the MD door assembly from the main body.

## Removing the holder assembly

- 1. Turn the holder assembly as shown in Fig.3.

- 2. Pull the side arm (L) marked a outward, then remove. Open the holder assembly as shown in Fig.4.

- 3. Move the U-shaped notch marked **b** in the direction of the arrow and release it from the shaft.

- 4. Move the part c inward and pull out the holder assembly from the shaft.

- ATTENTION: When reassembling, first reattach the part c to the shaft of the chassis assembly. And next, fit the U-shaped notch to the shaft.

U-shaped notch

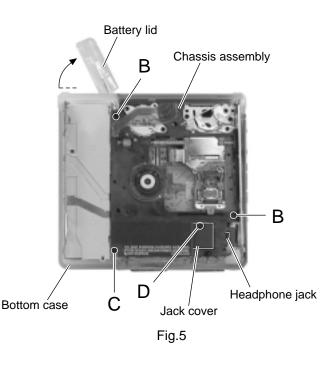

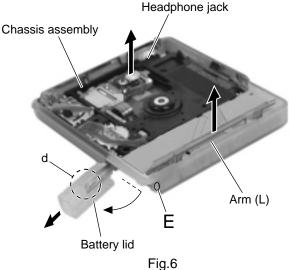

#### Removing the chassis assembly (See Fig.5 and 6)

- 1. Remove the two screws **B** and the one screw **C** attaching the chassis assembly. Remove the one screw **D** attaching the jack cover.

- 2. Open the battery lid and release the tab d from the chassis. Pull out the battery lid.

- 3. Remove the one screw **E** attaching the arm (L).

- 4. Remove the chassis assembly and the arm (L) while releasing them from the headphone jack on the bottom case.

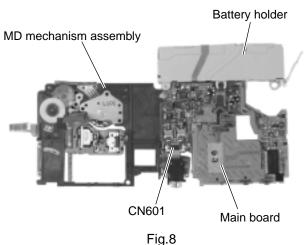

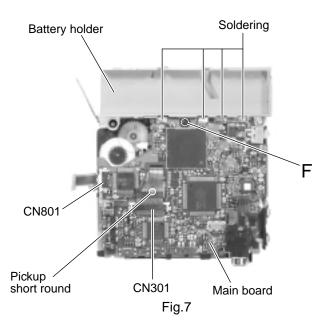

#### ■Removing the main P.W. board and the battery holder (See Fig.7 and 8)

- 1. Use a soldering bit provided with ground to solder or unsolder the short round.

- 2. Ground the set and the main board. The voltage level of the ground should be equal to that of the soldering bit.

- 3. Prevent static electricity using an earth band, etc.

- 4. Solder the short round of the pickup FPC for short circuit.

- 5. Disconnect the flexible wires from the connector CN301 and CN801 on the main board.

- 6. Remove the one screw **F** attaching the main board. Remove the main board and the battery holder, then reverse them.

- 7. Disconnect the flexible wire from connector CN601 on the main board.

- 8. Unsolder the soldered joint of the main board and the battery holder board.

#### <Removal of the MD mechanism>

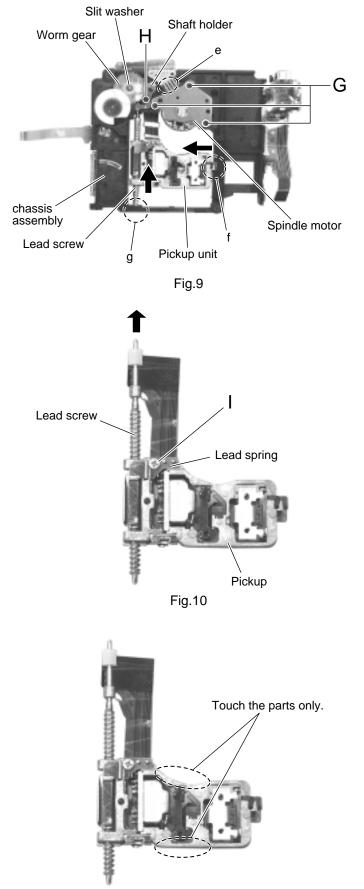

#### ■ Removing the spindle motor (See Fig.9)

- 1. Unsolder the part **e** of the flexible wire extending from the underside of the chassis assembly to the spindle motor. At this time, do not spill flux on the gear and others.

- 2. Remove the three screws **G** attaching the spindle motor and detach it from the chassis assembly.

#### ■Removing the pickup unit (See Fig.9)

- 1. Remove the slit washer and the worm gear from the underside of the chassis assembly.

- 2. Remove the screw H attaching the shaft holder, then detach the shaft.

- 3. Pull out the part **f** and **g** in the directions of the arrows to remove the pickup unit and the lead screw.

#### ■Removing the pickup (See Fig.10 and 11)

- 1. Remove the screw I attaching the lead spring, then detach the lead spring.

- 2. Pull out the shaft from the pickup.

ATTENTION: When handling the pickup unit, touch the parts marked in Fig.11 only.

Fig.11

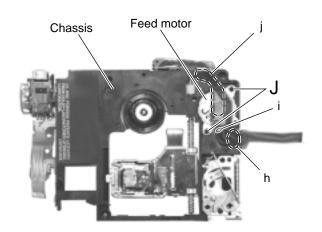

#### Removing the feed motor (See Fig.12)

- 1. Peel off the part **h** of the flexible wire on the underside of the feed motor.

- 2. Unsolder the solder joint **i** connecting the flexible wire to the feed motor.

- 3. Peel off the part **j** of the flexible wire.

- 4. Remove the two screws **j** attaching the feed motor on the upper side of the chassis assembly.

- ATTENTION: When reassembling, reattach the flexible wire with an adhesive tape and solder the appropriate part.

Fig.12

Switchi board assembly

Fig.13

#### Removing the switchi board assembly (See Fig.12)

- 1. Remove the switchi board assembly attached to the side of the chassis assembly with the double-sided tape.

- 2. When reassembling, reattach the switchi board assembly with an adhesive tape as before.

1-8

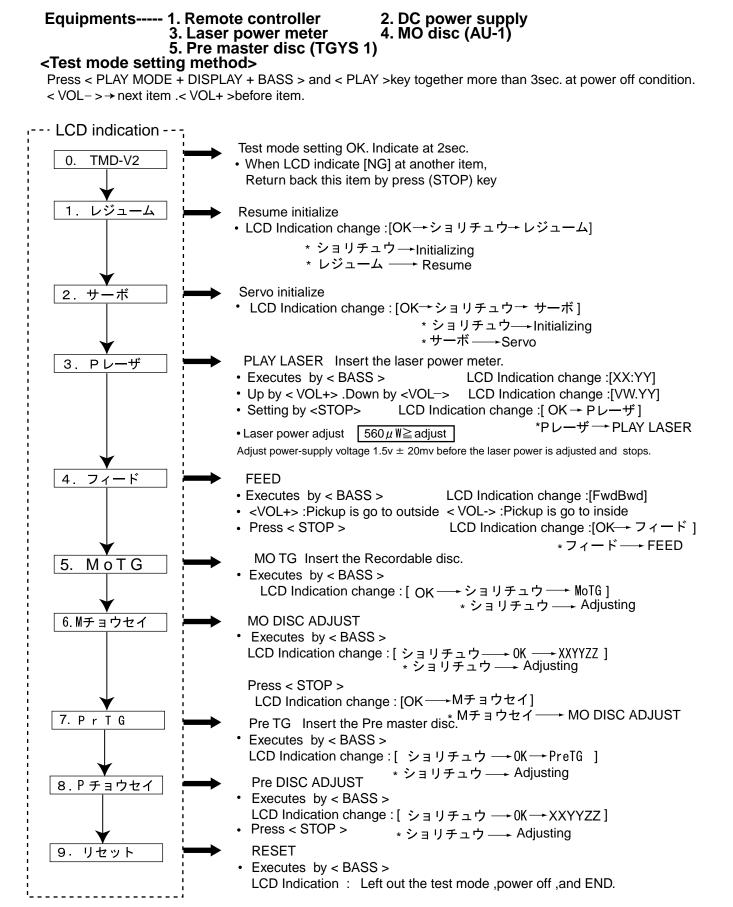

### Adjustment method

This model is auto adjustment by Remote Controller. Please adjust the attached remote controller.

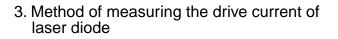

## Maintenance of laser pickup

#### 1. Cleaning of pickup lens

- (1) Prior to changing the pickup, clean the pickup lens.

- (2) For cleaning the lens, use the following cotton swab after mearsing it in alcohol.

Product No. JCB-B4; Manufacturer; Nippon Cotton Swab

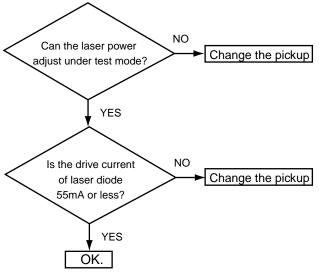

- Confirmation of the service life of laser diode when the service life of the laser diode has been exhausted, the following symptoms will appear.

- (1) The RF output (EFM output and eye pattern amplitude) will become lower.

- (2) The drive current required for light emitting of laser diode will be increased.

Confirm the service life according to the following flow chart:

When the voltage measured at the both side of carbon resistor R301 on the MD servo P.C. board (LVB20008) have become 12.1mV or over, the service life of the laser diode is judged to have been exhausted.

**Replacement of laser pickup**

Be sure to perform not only adjustment and operation of this system so carefully as not to directly look at the laser beam or touch on the body.

4. About Semi-solid state resistor of pick up

This is adjusted in the maker of pick up . Be careful please not to touch pick up .

## **Description of major ICs**

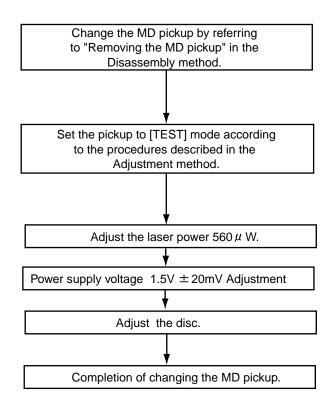

### ■ UPD784225GK-605(IC501) : CUP

1.Pin layout

#### 2.Function

| Pin<br>NO. | Symbol  | Function                               | Pin<br>NO. | Symbol  | Function                                   |

|------------|---------|----------------------------------------|------------|---------|--------------------------------------------|

| 1          | ANI5    | Connect to GND                         | 41         | -       | No connected                               |

| 2          | ANI6    | Connect to GND                         | 42         | -       | No connected                               |

| 3          | SPSEL   | No connected                           | 43         | -       | No connected                               |

| 4          | AVSS    | Connect to GND                         | 44         | -       | Test terminal                              |

| 5          | ACB     | Test terminal                          | 45         | -       | Test terminal                              |

| 6          | -       | No connected                           | 46         | -       | No connected                               |

| 7          | AVREF1  | Standard voltage for analog            | 47         | RFVCTL  | Test terminal                              |

| 8          | RMRX    | Remote control data input terminal     | 48         | PSAVE   | No connected                               |

| 9          | RMTX    | Remote control data output terminal    | 49         | RPON    | RP ON signal output terminal               |

| 10         | -       | No connected                           | 50         | DPON    | DP ON signal output terminal               |

| 11         | SRDT    | Serial data reading input              | 51         | REMOFF  | Remote control OFF signal output terminal  |

| 12         | SWDT    | Serial data writing input              | 52         | CS2     | Chip select 2                              |

| 13         | SCLK    | Serial bus clock output                | 53         | SCL     | Serial clock signal output terminal        |

| 14         | -       | No connected                           | 54         | DI      | Data output terminal                       |

| 15         | BEEP    | BEEP output                            | 55         | CS1     | Chip select 1                              |

| 16         | PSW     | Power ON/OFFoutput terminal            | 56         | MNT0    | Monitor 0 input terminal                   |

| 17         | MONDATA | Test terminal                          | 57         | MNT3    | Monitor 3 input terminal                   |

| 18         | MONCLK  | Test terminal                          | 58         | SENS    | DSP internal state input terminal          |

| 19         | XRST2   | Standby setting output terminal        | 59         | DO      | Data input terminal                        |

| 20         | TG      | Tracking gain setting terminal         | 60         | RESET   | Reset signal input terminal                |

| 21         | -       | No connected                           | 61         | XINT    | Interrupt status input terminal            |

| 22         | -       | No connected                           | 62         | SQSY    | Sync input terminal                        |

| 23         | XRST    | Reset signal output                    | 63         | -       | No connected                               |

| 24         | XLAT    | Serial bus latch output                | 64         | RPLY    | Remote control play detection terminal     |

| 25         | LVCTL   | LSI Power supply control signal output | 65         | DOOR    | Door open/close detection terminal         |

| 26         | LDON    | Laser diode ON signal output terminal  | 66         | PLAYKEY | PLAY key detection terminal                |

| 27         | RFOFF   | RF OFF signal output terminal          | 67         | VSS0    | Connect to GND                             |

| 28         | SLOFF   | SLED OFF signal output terminal        | 68         | VDD1    | Standard voltage terminal                  |

| 29         | -       | No connected                           | 69         | X2      | Connect to crystal oscillation             |

| 30         | MUTE    | Mute signal output terminal            | 70         | X1      | Connect to crystal oscillation             |

| 31         | POWER   | No connected                           | 71         | VPP     | Test terminal                              |

| 32         | DIR     | Test terminal                          | 72         | XT2     | No connected                               |

| 33         | DSS1    | Connects to GND                        | 73         | XT1     | Connect to GND                             |

| 34         | PS      | Standby mode output terminal           | 74         | VDD0    | Connect to GND                             |

| 35         | SS      | Start/Stop output terminal             | 75         | AVD0    | Standard voltage terminal                  |

| 36         | MON1    | Test terminal                          | 76         | KEY     | Remote control stop key detection terminal |

| 37         | MON2    | Test terminal                          | 77         | BATTERY | Battery voltage detection terminal         |

| 38         | MONXLAT | Test terminal                          | 78         | TEMP    | Connect to temperature detector            |

| 39         | -       | No connected                           | 79         | ANI3    | Connect to GND                             |

| 40         | -       | No connected                           | 80         | ANI4    | Connect to GND                             |

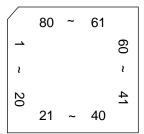

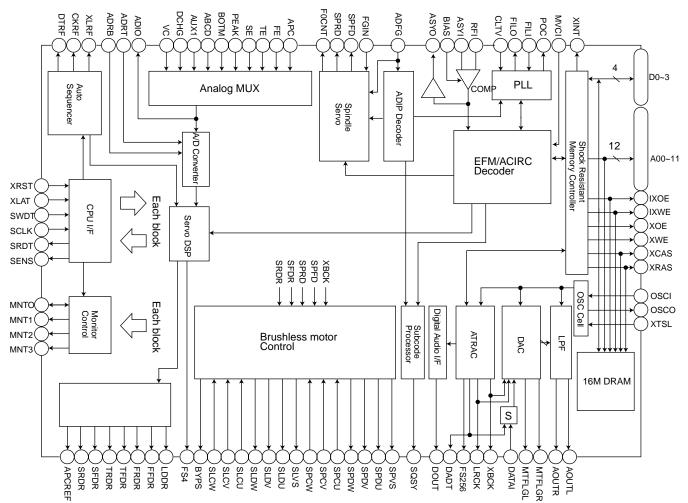

#### CXD2661GA-1 (IC351) : DSP

1. Pin layout

#### 2. Block diagram

2. Pin function (1/3)

|            |        | <b>(</b> · - <i>)</i> |                                                                                                                                            |  |  |  |  |  |

|------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin<br>no. | Symbol | I/O                   | Function                                                                                                                                   |  |  |  |  |  |

| 1          | VDCO   | -                     | VDD for internal logic (1.8V)                                                                                                              |  |  |  |  |  |

| 2          | MNT0   | I/O                   | Monitor input/output                                                                                                                       |  |  |  |  |  |

| 3          | MNT1   | 0                     | Monitor output                                                                                                                             |  |  |  |  |  |

| 4          | MNT2   | 0                     | Monitor output                                                                                                                             |  |  |  |  |  |

| 5          | MNT3   | 0                     | Monitor output                                                                                                                             |  |  |  |  |  |

| 6          | SWDT   | Ι                     | Microcomputer serial bus data writing input                                                                                                |  |  |  |  |  |

| 7          | SCLK   | Ι                     | Microcomputer serial bus clock input                                                                                                       |  |  |  |  |  |

| 8          | XLAT   | Ι                     | Microcomputer serial bus latch input                                                                                                       |  |  |  |  |  |

| 9          | VSCO   | -                     | GND for internal logic (1.8V)                                                                                                              |  |  |  |  |  |

| 10         | SRDT   | 0                     | Microcomputer serial bus data reading output                                                                                               |  |  |  |  |  |

| 11         | SENS   | 0                     | An internal state output to the address of the microcomputer serial bus.                                                                   |  |  |  |  |  |

| 12         | XRST   | Ι                     | Resets input "L"=reset                                                                                                                     |  |  |  |  |  |

| 13         | SQSY   | 0                     | PTGR=0 : ADIP sync output, PTGR=1 : DISC SUB-Q sync output                                                                                 |  |  |  |  |  |

| 14         | MTFLGL | 0                     | Lch 0 data detection flag output                                                                                                           |  |  |  |  |  |

| 15         | TST1   | Ι                     | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | XINT   | 0                     | Interrupt status output                                                                                                                    |  |  |  |  |  |

|            |        | Ι                     | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | VDIOSC | -                     | Vdd for OSC cell (2.4V)                                                                                                                    |  |  |  |  |  |

|            | OSCI   | Ι                     | X 'tal oscillation circuit input                                                                                                           |  |  |  |  |  |

|            | OSCO   | 0                     | X 'tal oscillation circuit output                                                                                                          |  |  |  |  |  |

| 21         | VSIOSC | -                     | GND for OSC cell                                                                                                                           |  |  |  |  |  |

|            | DAVSSL | -                     | Build in DAC GND (Lch)                                                                                                                     |  |  |  |  |  |

|            | VREFL  | 0                     | Built-in DAC VREF (Lch)                                                                                                                    |  |  |  |  |  |

|            | AOUTL  | 0                     | Built-in DAC Lch output                                                                                                                    |  |  |  |  |  |

|            | DAVDDL | -                     | Built-in DAC VDD (Lch 2.4V)                                                                                                                |  |  |  |  |  |

|            | DAVDDR | -                     | Built-in DAC VDD (Lch 2.4V)<br>Built-in DAC VDD (Lch 2.4V)                                                                                 |  |  |  |  |  |

|            | AOUTR  | 0                     | Built-in DAC Rch output                                                                                                                    |  |  |  |  |  |

|            | VREFR  | 0                     | Built-in DAC VREF (Rch)                                                                                                                    |  |  |  |  |  |

|            | DAVSSR | -                     | Built-inDAC GND (Rch)                                                                                                                      |  |  |  |  |  |

|            | VSC1   | -                     | GND for internal logic                                                                                                                     |  |  |  |  |  |

|            | TST9   | 1                     | Test terminal "H"                                                                                                                          |  |  |  |  |  |

| 32         |        |                       | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | TST4   | -                     | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | DOUT   | 0                     | Digital audio output                                                                                                                       |  |  |  |  |  |

|            | NC     | -                     | OPEN                                                                                                                                       |  |  |  |  |  |

|            | VDC1   | -                     | VDD for internal logic. (1.8V)                                                                                                             |  |  |  |  |  |

|            | VDC2   | -                     | VDD for internal logic. (1.8V)                                                                                                             |  |  |  |  |  |

|            | DATA1  | Ι                     | External audio data input terminal to internal DAC                                                                                         |  |  |  |  |  |

|            | TST5   | -                     | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | TST6   |                       | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | TST7   |                       | Test terminal "L"                                                                                                                          |  |  |  |  |  |

|            | DADT   | 0                     | Data output to external D/A converter                                                                                                      |  |  |  |  |  |

|            | LRCK   | 0                     | LR clock for external D/A converter (44.1kHz)                                                                                              |  |  |  |  |  |

|            | VSC2   | -                     | GND for internal logic. (1.8V)                                                                                                             |  |  |  |  |  |

|            | XBCK   | 0                     | Bit clock for external D/A converter (2.8224MHz)                                                                                           |  |  |  |  |  |

|            | F256   | 0                     |                                                                                                                                            |  |  |  |  |  |

|            |        | 0                     | 11.2896MHz clock output (X'tal)                                                                                                            |  |  |  |  |  |

|            | A03    |                       | Address output for external DRAM When external DRAM is not used, OPEN.                                                                     |  |  |  |  |  |

|            | A04    | 0                     | Address output for external DRAMWhen external DRAM is not used, OPEN.Address output for external DRAMWhen external DRAM is not used, OPEN. |  |  |  |  |  |

|            | A02    |                       | •                                                                                                                                          |  |  |  |  |  |

| 50         | A05    | 0                     | Address output for external DRAM When external DRAM is not used, OPEN.                                                                     |  |  |  |  |  |

#### 2. Pin function (2/3)

| Din        |        | ,   |                                                                                       |  |  |  |  |  |

|------------|--------|-----|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin<br>no. | Symbol | I/O | Function                                                                              |  |  |  |  |  |

| 51         | A01    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 52         | A06    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 53         | VDIO1  | -   | VDD for I/O cell (2.4V)                                                               |  |  |  |  |  |

| 54         | VSIO1  | -   | GND for I/O cell                                                                      |  |  |  |  |  |

| 55         | A00    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 56         | A07    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 57         | A10    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 58         | A08    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 59         | A09    | 0   | Address output for external DRAM When external DRAM is not used, OPEN.                |  |  |  |  |  |

| 60         | XRAS   | 0   | RAS output for external DRAM When external DRAM is not used, OPEN.                    |  |  |  |  |  |

| 61         | IXOE   | 0   | Open                                                                                  |  |  |  |  |  |

| 62         | IXWE   | 0   | Open                                                                                  |  |  |  |  |  |

| 63         | XCAS   | 0   | CAS output for external DRAM When external DRAM is not used, OPEN.                    |  |  |  |  |  |

| 64         | D1     | I/O | Data I/O for external DRAM When external DRAM is not used, OPEN.                      |  |  |  |  |  |

| 65         | D2     | I/O | Data I/O for external DRAM When external DRAM is not used, OPEN.                      |  |  |  |  |  |

| 66         | D0     | I/O | Data I/O for external DRAM When external DRAM is not used, OPEN.                      |  |  |  |  |  |

| 67         | D3     | I/O | Data I/O for external DRAM When external DRAM is not used, OPEN.                      |  |  |  |  |  |

| 68         | VDC3   | -   | VDD for 1.8V internal logic                                                           |  |  |  |  |  |

| 69         | VSC3   | -   | VSS for 1.8V internal logic                                                           |  |  |  |  |  |

| 70         | A11    | 0   | Open                                                                                  |  |  |  |  |  |

| 71         | XOE    | 0   | Output enable output for external DRAM When external DRAM is not used, OPEN.          |  |  |  |  |  |

| 72         | XWE    | 0   | Write enable output for external DRAM When external DRAM is not used, OPEN.           |  |  |  |  |  |

| 73         | MVCI   | 1   | Clock input from external VCO                                                         |  |  |  |  |  |

| 74         | ASYO   | 0   | Playback EFM binarization signal output                                               |  |  |  |  |  |

| 75         | ASYI   | -   | Playback EFM comparator slice level input                                             |  |  |  |  |  |

| 76         | AVD1   | I   | Analog power supply (2.4V)                                                            |  |  |  |  |  |

| 77         | BIAS   | 1   | Playback EFM comparator bias current input                                            |  |  |  |  |  |

| 78         | RFI    | 1   | Playback EFM RF signal input                                                          |  |  |  |  |  |

| 79         | AVS1   | -   | Analog GND                                                                            |  |  |  |  |  |

| 80         | PCO    | 0   | Phase comparison output for playback EFM system mastering PLL                         |  |  |  |  |  |

| 81         | FILI   |     | Filter input for playback EFM system mastering PLL                                    |  |  |  |  |  |

| 82         | FILO   | 0   | Filter output for playback EFM system mastering PLL                                   |  |  |  |  |  |

| 83         | CLTV   | 1   | Internal VCO control voltage input for playback EFM system mastering PLL              |  |  |  |  |  |

| 84         | PEAK   | •   | Peak holding input of optical amount signal (From CXA2523AR)                          |  |  |  |  |  |

| 85         | BOTM   | -   | Bottom holding input of optical amount signal                                         |  |  |  |  |  |

| 86         | ABCD   |     | Optical amount signal input (From CXA2523AR)                                          |  |  |  |  |  |

| 87         | FE     | •   |                                                                                       |  |  |  |  |  |

| 88         | AUX1   |     | Focus error signal input (From CXA2523AR)                                             |  |  |  |  |  |

| 89         | VC     | 1   | Assistance A/D input (when not using .connect to analog power supply)                 |  |  |  |  |  |

|            | ADIO   | 0   | Middle point voltage input (From CXA2523AR)                                           |  |  |  |  |  |

| 90         | ADRT   |     | Open                                                                                  |  |  |  |  |  |

| 91         |        | 1   | A/D converter operation range upper bound voltage input<br>Analog power supply (2.4V) |  |  |  |  |  |

| 92         | AVD2   | -   |                                                                                       |  |  |  |  |  |

| 93         | AVS2   | -   | Analog GND                                                                            |  |  |  |  |  |

| 94         | ADRB   |     | A/D converter operation range lower bound voltage input                               |  |  |  |  |  |

| 95         | SE     |     | SLED error input (From CXA2523AR)                                                     |  |  |  |  |  |

| 96         |        |     | Tracking error input (From CXA2523AR)                                                 |  |  |  |  |  |

| 97         | DCHG   |     | Connects with an analog power supply of low impedance                                 |  |  |  |  |  |

| 98         | APC    |     | Error signal input for laser digital APC (From CXA2523AR)                             |  |  |  |  |  |

| 99         | ADFG   |     | ADIP binary-coded FM signal input (22.05 1kHz) (From CXA2523)                         |  |  |  |  |  |

| 100        | VDIO2  | -   | VDD for I/O (2.4V)                                                                    |  |  |  |  |  |

2. Pin function (3/3)

| Dia               | - ( | ,                                                         |  |  |  |

|-------------------|-----|-----------------------------------------------------------|--|--|--|

| Pin<br>no. Symbol | I/O | Function                                                  |  |  |  |

| 101 VSIO2         | -   | VSS for I/O (2.4V)                                        |  |  |  |

| 102 F0CON         | ТΟ  | Filter cutting off control output of CXA2523              |  |  |  |

| 103 XLRF          | 0   | Latch output for CXA2523 control                          |  |  |  |

| 104 CKRF          | 0   | ock output for CXA2523 control                            |  |  |  |

| 105 DTRF          | 0   | a output for CXA2523 control                              |  |  |  |

| 106 APCRE         | FO  | Reference PWM output for laser APC                        |  |  |  |

| 107 LDDR          | 0   | PWM output for laser digital APC                          |  |  |  |

| 108 VDC4          | -   | VDD for internal logic (1.8V)                             |  |  |  |

| 109 TRDR          | 0   | Tracking servo drive PWM output (-)                       |  |  |  |

| 110 TFDR          | 0   | Tracking servo drive PWM output (+)                       |  |  |  |

| 111 FFDR          | 0   | Focus servo drive PWM output (+)                          |  |  |  |

| 112 FRDR          | 0   | Focus servo drive PWM output (-)                          |  |  |  |

| 113 FS4           | 0   | 176.4KHZ clock output (X 'tal)                            |  |  |  |

| 114 SRDR          | 0   | SLED servo drive PWM output (-)                           |  |  |  |

| 115 SFDR          | 0   | SLED servo drive PWM output (+)                           |  |  |  |

| 116 VSC4          | -   | GND for internal logic                                    |  |  |  |

| 117 SPRD          | 0   | Spindle servo drive output (PWM - or polarity)            |  |  |  |

| 118 SPFD          | 0   | Spindle servo drive output (PWM + or PWM absolute value)  |  |  |  |

| 119 FGIN          | 1   | FG input for spindle CAV servo                            |  |  |  |

| 120 TESTI         | 1   | Test input. Connects to GND.                              |  |  |  |

| 121 TEST2         | 1   | Test input. Connects to GND.                              |  |  |  |

| 122 TEST3         | 1   | Test input. Connects to GND.                              |  |  |  |

| 123 MTFLGF        | २ ० | Rch 0 data detection flag output                          |  |  |  |

| 124 SPVS          | 0   | Brush less spindle moter Absolute value PWM output        |  |  |  |

| 125 VDIO3         | -   | VDD for I/O cell (2.4V)                                   |  |  |  |

| 126 VSIO3         | -   | VSS for I/O cell                                          |  |  |  |

| 127 SPDU          | 0   | Brush less spindle moter three phases drive logic output. |  |  |  |

| 128 SPDV          | 0   | Brush less spindle moter three phases drive logic output. |  |  |  |

| 129 SPDW          | 0   | Brush less spindle moter three phases drive logic output. |  |  |  |

| 130 SPCU          |     | Brush less spindle moter drive comparate input.           |  |  |  |

| 131 SPCV          | 1   | Brush less spindle moter drive comparate input.           |  |  |  |

| 132 SPCW          | 1   | Brush less spindle moter drive comparate input.           |  |  |  |

| 133 SLDU          | 0   | Brush less SLED moter three phases drive logic output.    |  |  |  |

| 134 SLDV          | 0   | Brush less SLED moter three phases drive logic output.    |  |  |  |

| 135 SLDW          | 0   | Brush less SLED moter three phases drive logic output.    |  |  |  |

| 136 VDC5          | -   | VDD for internal logic.                                   |  |  |  |

| 137 VSC5          | -   | GND for internal logic.                                   |  |  |  |

| 138 SLCU          |     | Brush less SLED moter three phases drive comparate input. |  |  |  |

| 139 SLCV          |     | Brush less SLED moter three phases drive comparate input. |  |  |  |

| 140 SLCW          | I/O | Brush less SLED moter three phases drive comparate input. |  |  |  |

| 141 SLVS          | 0   | Brush less SLED moter absolute value PWM output.          |  |  |  |

| 142 BYPS          | 0   | Brush less SLED moter supplementary output.               |  |  |  |

| 143 DVSS0         | -   | GND for built-in 16 M bits DRAM                           |  |  |  |

| 144 DVDDO         | -   | VDD for built-in 16 M bits DRAM. (2.4V)                   |  |  |  |

| 145 DVSS1         | -   | GND for built-in 16 M bits DRAM.                          |  |  |  |

| 146 DVDD1         | -   | VDD for built-in 16 M bits DRAM. (2.4V)                   |  |  |  |

| 147 TST8          | -   | OPEN                                                      |  |  |  |

|                   |     |                                                           |  |  |  |

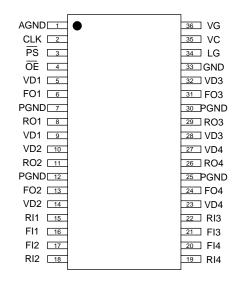

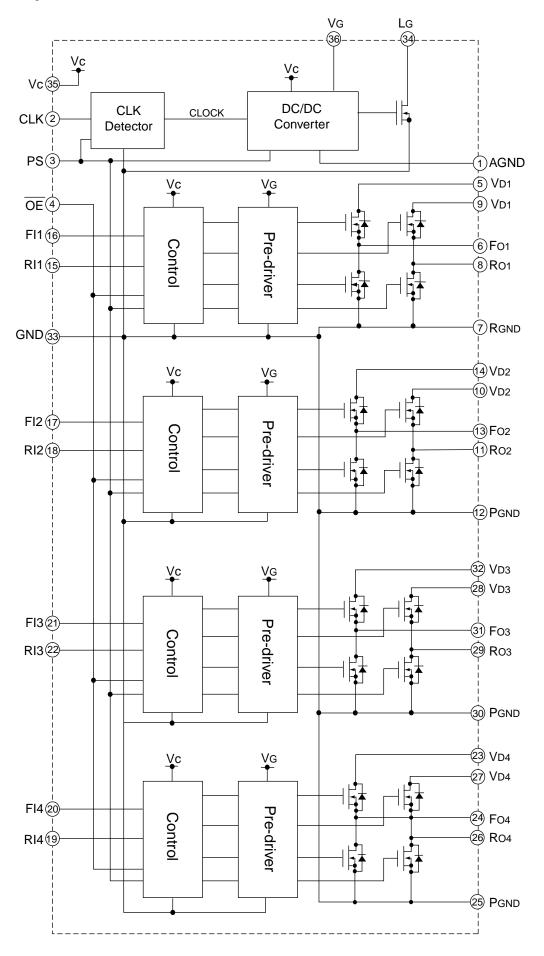

#### MPC17A139MTB-X (IC400) : 4ch bridge driver

#### 1. Pin layout

#### 2. Pin function

#### Clock detector

| CLK | PS | OSC.circuit     |

|-----|----|-----------------|

| Х   | Н  | Auto            |

|     | Н  | Synchronization |

| Х   | L  | Stop            |

#### Driver

| PS, | OE | INP | UT | OUTPI | JT 1~4 |

|-----|----|-----|----|-------|--------|

| PS  | OE | FI  | RI | FO    | RO     |

| н   | L  | L   | L  | L     | L      |

| н   | L  | L   | Н  | L     | Н      |

| н   | L  | Н   | L  | Н     | L      |

| н   | L  | Н   | н  | L     | L      |

| н   | Н  | Х   | х  | L     | L      |

| L   | Х  | Х   | Х  | Z     | Z      |

X:Don't care

Z:High impedance

MPC17A139MTB-X

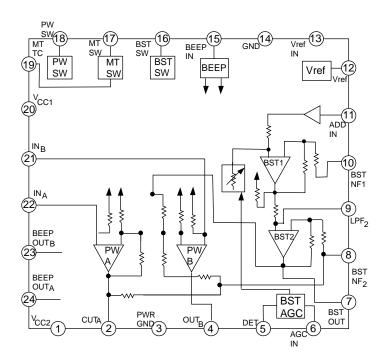

#### ■CXA2588R (IC300) : RF amp. ) ADAGC CSLED 1. Pin layout & block diagram BOTM ABCD ADFG ADFM ADIN AUX Ш SЕ Щ 33-32 (36) (35) (34) (31) (30) -(29) 28 -(27) (26) ADIP Amp TE/SE Amp Peak, Bottom Detector PEAK (37 (24) Vcc FE Amp (38) RF (23) 3TADJ AGC,EQ RFAGC (39) (22) EQADJ AGCI (40) (21) VREF NC (41) (20) F0CNT NC (42) (19) XSTBY ADDC (43 (18) XLAT CPU Command I/F NC (44) (17) SCLK **3T Detector** ABCD Amp 0/-2dB TEGC (45 16) SWDT RFO (46) RF Amp (15) OP IN OP Amp MORFI (47) (14) OP OUT MORFO (48) (13) GND I-V Amp I-V Amp APC 2 APC (1) 1 3 2 2 APCREF (1) 5 8 9 6 PD ш Ū Δ ш Ľ. ∢

#### 2.Pin function

| Pin<br>No. | Symbol | I/O | Function                                             | Pin<br>No. | Symbol | I/O | Function                                                         |

|------------|--------|-----|------------------------------------------------------|------------|--------|-----|------------------------------------------------------------------|

| 1          | I      | Ι   | I-V converted RF signal I input                      | 25         | WBLADJ | I/O | BPF3T IF setting terminal                                        |

| 2          | J      | Ι   | I-V converted RF signal J input                      | 26         | TE     | 0   | Tracking error signal output terminal                            |

| 3          | VC     | 0   | Vcc/2 voltage output                                 | 27         | CSLED  | 1   | Sled error signal LPF capacitor connect terminal                 |

| 4          | А      | Ι   | A current input for main beam servo signal           | 28         | SE     | 0   | Sled error signal output terminal                                |

| 5          | В      | Ι   | B current input for main beam servo signal           | 29         | ADFM   | 0   | ADIP FM signal output terminal                                   |

| 6          | С      | Ι   | C current input for main beam servo signal           | 30         | ADIN   | Τ   | ADIP signal completer input terminal                             |

| 7          | D      | Ι   | D current input for main beam servo signal           | 31         | ADAGC  | -   | ADIP AGC capacitor connect terminal                              |

| 8          | Е      | Ι   | E current input for side beam servo signal           | 32         | ADFG   | 0   | ADIP binary signal output                                        |

| 9          | F      | Ι   | F current input for side beam servo signal           | 33         | AUX    | 0   | 13 output/temp.signal output                                     |

| 10         | PD     | Ι   | Reflection light q'ty monitor signal input           | 34         | FE     | О   | Focus error signal output                                        |

| 11         | APC    | 0   | Laser APC output                                     | 35         | ABCD   | О   | Reflection light q'ty signal output for main beam servo detector |

| 12         | APCREF | Ι   | Ref. voltage input for laser power intensity setting | 36         | BOTM   | О   | RF/ABCD bottom-hold signal output                                |

| 13         | GND    | -   | Ground                                               | 37         | PEAK   | 0   | RF/ABCD peak-hold signal output                                  |

| 14         | OPOUT  | 0   | Ope. amp output terminal                             | 38         | RF     | 0   | RF equalizer output                                              |

| 15         | OPIN   | Ι   | 21dB ope. amp input terminal                         | 39         | RFAGC  | -   | RFAGC capacitor connection                                       |

| 16         | SWDT   | Ι   | Serial data input terminal                           | 40         | AGCI   | Ι   | RFAGC input                                                      |

| 17         | SCLK   | Ι   | Shift clock input terminal                           | 41         | NC     | -   | Non connect                                                      |

| 18         | XLAT   | Ι   | Latch input terminal                                 | 42         | NC     | -   | Non connect                                                      |

| 19         | XSTBY  | Ι   | Stand by setting terminal                            | 43         | ADDC   | I/O | ADIP amp. feedback circuit capacitor connection                  |

| 20         | F0CNT  | Ι   | F0 count setting terminal                            | 44         | NC     | -   | Non connection                                                   |

| 21         | VREF   | 0   | Reference voltage output terminal                    | 45         | TEGC   | Τ   | TE amp. gain switching                                           |

| 22         | EQADJ  | I/O | EQ IF setting terminal                               | 46         | RFO    | 0   | RF amp. output                                                   |

| 23         | 3TADJ  | I/O | BPF3T IF setting terminal                            | 47         | MORFI  | Ι   | Groove RF signal AC-coupled input                                |

| 24         | Vcc    | -   | Power supply                                         | 48         | MORFO  | 0   | Groove RF signal output                                          |

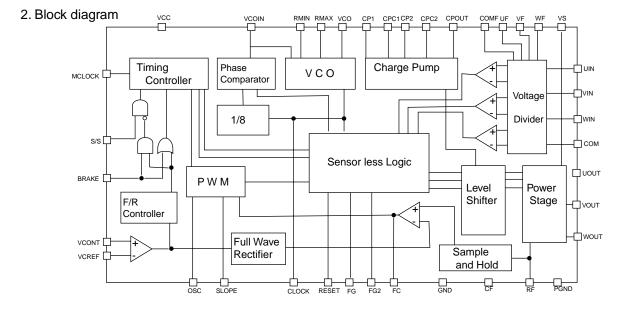

#### JCV8002-W (IC601) : Head phone amp

1. Pin layout

#### 2. Block diagram

#### 3. Pin function

| Pin<br>no. | Symbol           | FUNCTION                                                                                     |

|------------|------------------|----------------------------------------------------------------------------------------------|

| 1          | VCC2             | V <sub>CC2</sub> (+B) in power amplifier output steps                                        |

| 2          | OUTA             | Power amplifier output                                                                       |

| 3          | PWR GND          | GND in power amplifier output steps                                                          |

| 4          | OUTB             | Power amplifier output                                                                       |

| 5          | DET              | Smoothness of level detection of boost AGC                                                   |

| 6          | AGC IN           | BST amplifier input signal level variable control by input lever to boost AGC input terminal |

| 7          | BST OUT          | Output terminal of BST amplifier2                                                            |

| 8          | BST NF2          | Terminal NF of BST amplifier2                                                                |

| 9          | LPF <sub>2</sub> | Output BST amplifier1                                                                        |

| 10         | BST NF1          | NF of BST amplifier1                                                                         |

| 11         | ADD IN           | ADD amplifier input                                                                          |

| 12         | Vref             | Standard potential circuit                                                                   |

| 13         | VrefIN           | Standard potential circuit                                                                   |

| 14         | GND              | Power part input steps GND                                                                   |

|            | BEEP IN          | Beep input terminal                                                                          |

| 16         | BST SW           | Beep output terminal                                                                         |

| 17         | MT SW            | Mute switch                                                                                  |

| 18         | PW SW            | Power On/OFF switch                                                                          |

| 19         | MT TC            | Mute smoothing Power mute switch                                                             |

| 20         | V <sub>CC1</sub> | Main parts V <sub>CC</sub>                                                                   |

| 21         | IN B             | Power amplifier input                                                                        |

| 22         | IN A             | Power amplifier input                                                                        |

| 23         | BEEP OUT B       | Beep output terminal                                                                         |

| 24         | BEEP OUT A       | Beep output terminal                                                                         |

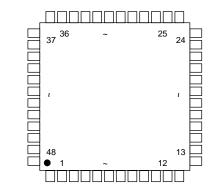

#### CXA8069M (IC450) : Sensoorless moter driver

#### 3. Pin function

| Pin |        | <b>F</b> (:                                        | Pin |        |                                                       |

|-----|--------|----------------------------------------------------|-----|--------|-------------------------------------------------------|

| no. | Symbol | Function                                           | no. | Symbol | Function                                              |

| 1   | NC     |                                                    | 25  | VCOIN  | For controlling frequency of VCO                      |

| 2   | RF     | For monitoring motor current                       | 26  | CLOCK  | For CLOCK signal monitor                              |

| 3   | VS     | For supplying the voltage to the power stage       | 27  | GND    |                                                       |

| 4   | NC     |                                                    | 28  | CF     | For sample and hold circuit to mesasure motor current |

| 5   | CPC1   | For connecting to the first charge pump capacitor  | 29  | OSC    | For oscillating sawtooth PWM                          |

| 6   | CP1    | For connecting to the first charge pump capacitor  | 30  | SLOPE  | For oscillating sawtooth for soft-switching           |

| 7   | CPC2   | For connecting to the second charge pump capacitor | 31  | MCLOCK | For input of clock                                    |

| 8   | CP2    | For connecting to the second charge pump capacitor | 32  | VCC    | For supplying the voltage except the power section    |

| 9   | CPOUT  | For connecting to the third charge pump capacitor  | 33  | NC     |                                                       |

| 10  | GND    | For GND except the power section                   | 34  | VS     | For supplying the voltage to the power stage          |

| 11  | S/S    | For start and stop                                 | 35  | RF     | For monitoring motor current                          |

| 12  | BRAKE  | For brake                                          | 36  | NC     |                                                       |

| 13  | VCONT  | For controlling velocity                           | 37  | RESET  | For resetting register                                |

| 14  | VCREF  | For reference to control velocity                  | 38  | WIN    | For sensing back electro magnetic force of coils      |

| 15  | FG     | For FG output                                      | 39  | WOUT   | For output                                            |

| 16  | FG2    | For FG output of dividing Pin15 signal by 2        | 40  | NC     |                                                       |

| 17  | FC     | For control amp phase compensation                 | 41  | VIN    | For sensing back electro magnetic force of coils      |

| 18  | VCO    | For setting oscilation frequency of VCO            | 42  | VOUT   | For output                                            |

| 19  | RMAX   | For setting max.frequency of VCO                   | 43  | NC     |                                                       |

| 20  | RMIN   | For setting min.frequency of VCO                   | 44  | NC     |                                                       |

| 21  | COMF   | For shaping waveform of motor voltage              | 45  | UIN    | For sensing back electro magnetic force of coils      |

| 22  | WF     | For shaping waveform of motor voltage              | 46  | UOUT   | For output                                            |

| 23  | VF     | For shaping waveform of motor voltage              | 47  | COM    | For the common voltage sensing                        |

| 24  | UF     | For shaping waveform of motor voltage              | 48  | PGND   | For the GND for power stage guarding                  |

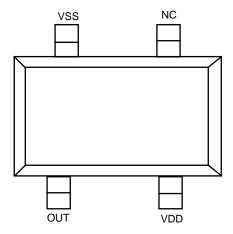

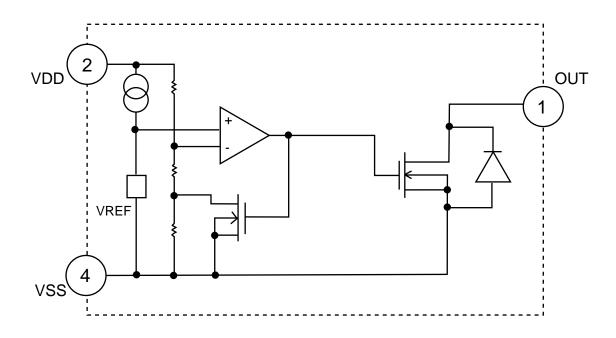

#### S-80822ANNP-W (IC504) : Reset switch

1.Pin layout

#### 2.Block daiagram

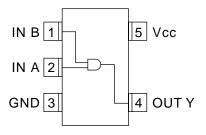

#### TC7S08FU-X (IC2) : Regulator

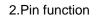

1.Pni layout

2.Pin function

| Pin<br>No. | Symbol | Function       |

|------------|--------|----------------|

| 1          | IN B   | Input voltage  |

| 2          | IN A   | Input voltage  |

| 3          | GND    | Ground         |

| 4          | OUT Y  | Output voltage |

| 5          | Vcc    | Power supply   |

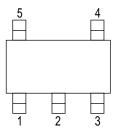

### **XC6367A241M-X (IC901)** : Regulator

1. Pin layout

#### 2. Pin function

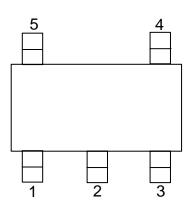

| Pin<br>No. | Symbol | Function                       |

|------------|--------|--------------------------------|

| 1          | VOUT   | Voltage output                 |

| 2          | VDD    | Power supply                   |

| 3          | CE     | Chip enable                    |

| 4          | GND    | Ground                         |

| 5          | EXT    | External transistor connection |

#### 3. Block diagram

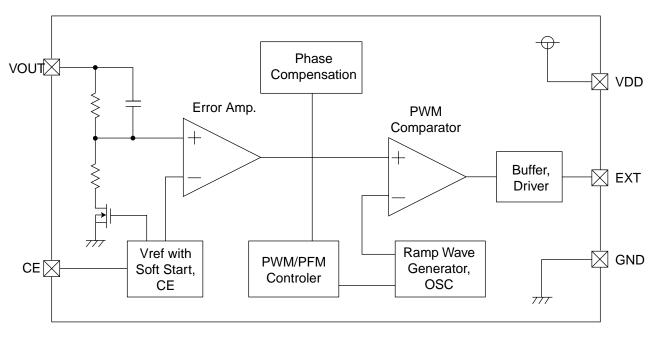

#### XC6367B101M-X (IC461,IC902,IC941) : Regulator

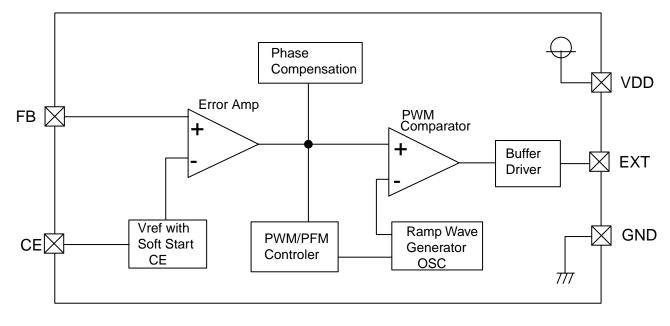

#### 1.Pin layout

| Pin NO. | Symbol | Function                       |

|---------|--------|--------------------------------|

| 1       | FB     | Output voltage feed back input |

| 2       | VDD    | Power supply                   |

| 3       | CE     | Chip enable                    |

| 4       | GND    | Ground                         |

| 5       | EXT    | External transistor connection |

3.Block diagram

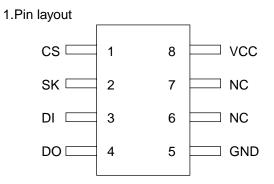

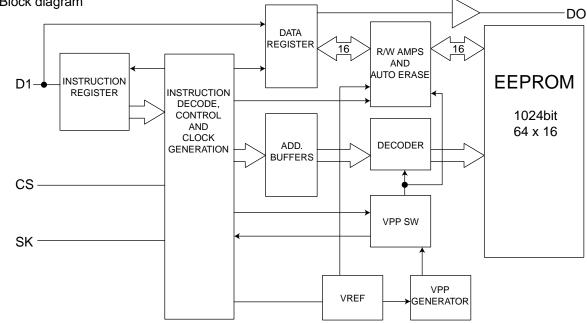

#### ■ AK93C45BH-W (IC502,IC503) : EEPROM

2.Pin function

| Symbol | Function     |

|--------|--------------|

| CS     | Chip select  |

| SK     | Clock input  |

| DI     | Data input   |

| DO     | Data output  |

| Vcc    | Poser supply |

| GND    | Ground       |

| NC     | Non connect  |

#### 3.Block diagram

VICTOR COMPANY OF JAPAN, LIMITED AUDIO & COMMUNICATION BUSINESS DIVISION PERSONAL & MOBILE NETWORK B.U. 10-1,1Chome,Ohwatari-machi,Maebashi-city,371-8543,Japan